SD協(xié)議分析儀費(fèi)用

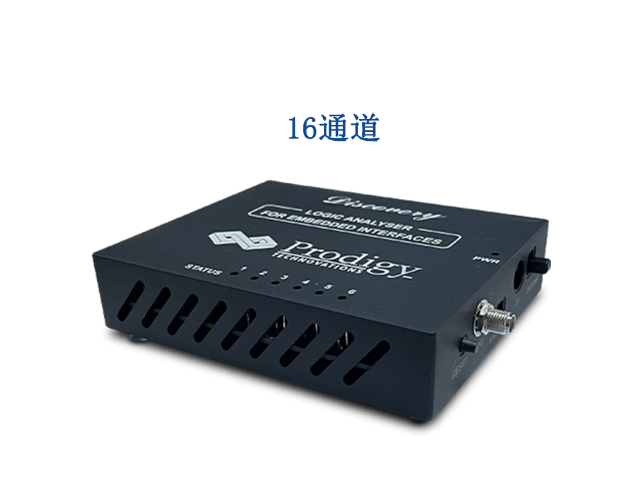

影響邏輯分析儀的正常使用的問題。針對(duì)上述提出的問題,在原有的邏輯分析儀基礎(chǔ)上進(jìn)行創(chuàng)新設(shè)計(jì)。技術(shù)實(shí)現(xiàn)要素:解決的技術(shù)問題針對(duì)現(xiàn)有技術(shù)的不足,本實(shí)用新型提供了一種便于散熱通風(fēng)的邏輯分析儀,解決了現(xiàn)有的部分邏輯分析儀常放置于機(jī)房?jī)?nèi)或工作室內(nèi),且邏輯分析儀處于相對(duì)封閉的狀態(tài),使得邏輯分析儀內(nèi)部的組件在工作中產(chǎn)生的熱量無(wú)法很好地排出,導(dǎo)致邏輯分析儀內(nèi)部溫度較高,影響邏輯分析儀的正常使用的問題。技術(shù)方案為實(shí)現(xiàn)上述目的,本實(shí)用新型提供如下技術(shù)方案:一種便于散熱通風(fēng)的邏輯分析儀,包括邏輯分析儀本體歐奧電子是Prodigy在中國(guó)區(qū)的官方授權(quán)合作伙伴,ProdigyMPHY,UniPro,UFS總線協(xié)議分析儀測(cè)試解決方案不會(huì)收到EAR進(jìn)出口方面的管制。同時(shí)還有代理其他總類的協(xié)議分析儀,包括嵌入式設(shè)備用的SDIO協(xié)議分析儀,QSPI協(xié)議分析儀及訓(xùn)練器,I3C協(xié)議分析儀及訓(xùn)練器,RFFE協(xié)議分析儀及訓(xùn)練器等等。我司還有代理SPMI協(xié)議分析儀及訓(xùn)練器,車載以太網(wǎng)分析儀,以及各種相關(guān)的基于示波器的解碼軟件和SI測(cè)試軟件。同時(shí),歐奧電子也有提供高難度焊接,以及高速信號(hào),如UFS,DDR3/DDR4,USBtypeC等高速協(xié)議抓取和分析的服務(wù)。邏輯分析儀哪家強(qiáng)?歐奧強(qiáng)!SD協(xié)議分析儀費(fèi)用

歐奧電子也有提供高難度焊接,以及高速信號(hào),如UFS,DDR3/DDR4,USBtypeC等高速協(xié)議抓取和分析的服務(wù)。通過在整個(gè)信號(hào)活動(dòng)信封內(nèi)執(zhí)行全時(shí)掃描,眼定位可以顯示在時(shí)間和電壓的小窗口中檢測(cè)到的轉(zhuǎn)變。這些掃描稱為眼圖掃描(eyescan)。像示波器一樣,眼圖掃描用于顯示測(cè)量數(shù)據(jù)。每個(gè)窗口中的轉(zhuǎn)變數(shù)量都會(huì)突出顯示。這可以使概覽眼型圖案,并確定是否需要使用示波器來進(jìn)一步詳細(xì)地查看信號(hào)。圖19眼圖掃描可以運(yùn)行導(dǎo)致自動(dòng)設(shè)置閾電壓和采樣位置的eyescan,或運(yùn)行只導(dǎo)致自動(dòng)設(shè)置采樣位置的eyescan。眼定位測(cè)量收集數(shù)據(jù)所基于的通道數(shù)量會(huì)影響測(cè)量時(shí)間。當(dāng)一個(gè)模塊中存在多個(gè)邏輯分析儀卡時(shí)將出現(xiàn)異常;在這種情況下,測(cè)量將同時(shí)并行運(yùn)行。支持差分信號(hào)的邏輯分析儀中的眼圖掃描EyeScan:支持差分信號(hào)的邏輯分析儀(如16962A邏輯分析儀模塊)針對(duì)輸入使用真值差分接收器:可編程參考電壓將計(jì)入負(fù)輸入。這是分析儀采用單端探頭時(shí)的閾電壓。對(duì)于差分探測(cè)的相關(guān)操作,通常將參考電壓編寫為0V:隨后將接收器的輸出與0V進(jìn)行比較,從差分輸入信號(hào)產(chǎn)生內(nèi)部邏輯信號(hào)。請(qǐng)注意。云浮USB協(xié)議分析儀售價(jià)分析儀廠家哪家好?歐奧電子好!

還要對(duì)信號(hào)進(jìn)行放,因?yàn)閭鬟f過來的信號(hào)幅度比較小。圖23探頭的信號(hào)完整性考慮探頭的負(fù)載效應(yīng)主要分為兩種類型:直流負(fù)載和交流負(fù)載。直流負(fù)載:探頭看起來象一個(gè)對(duì)地的直流負(fù)載,一般是20K歐姆。如果被測(cè)總線具有弱上拉或弱下拉特性(即上下拉電阻較),這個(gè)負(fù)載可能會(huì)導(dǎo)致邏輯錯(cuò)誤。直流負(fù)載主要由探頭尖的電阻決定,這個(gè)電阻阻值越,直流負(fù)載越小,阻值越小,直流負(fù)載越。交流負(fù)載:探頭包含寄生電容和電感。這些寄生參數(shù)會(huì)減小探頭帶寬和導(dǎo)致信號(hào)反射。我們需要在被測(cè)電路接收端和探頭尖處考慮信號(hào)完整性。探頭帶寬被降低主要來自2個(gè)方面:探頭電容和探頭與目標(biāo)連接的連線的電容。探頭導(dǎo)致信號(hào)反射的原因是4個(gè)方面:探頭電容和電感;探頭在被測(cè)總線上的探測(cè)位置;總線的拓?fù)浣Y(jié)構(gòu);探頭和目標(biāo)間連線的長(zhǎng)度。對(duì)于交流負(fù)載,我們需要考慮:探測(cè)點(diǎn)在傳輸線的位置,總線的拓?fù)浣Y(jié)構(gòu)和探頭和目標(biāo)間連線的長(zhǎng)度。探頭的負(fù)載除了可以用復(fù)雜的Spice模型仿真分析外,也可以用簡(jiǎn)單的RC模型簡(jiǎn)單預(yù)估負(fù)載效應(yīng)。下圖是典型探頭的RC模型。圖24常用探頭的RC模型我們需要仔細(xì)考慮探頭和目標(biāo)之間的連線。為了可靠的電氣連接,有三種方式可選擇:短線探測(cè)(StubProbing),阻尼電阻探測(cè)。

歐奧電子是Prodigy在中國(guó)區(qū)的官方授權(quán)合作伙伴,ProdigyMPHY,UniPro,UFS總線協(xié)議分析儀測(cè)試解決方案不會(huì)收到EAR進(jìn)出口方面的管制。同時(shí)還有代理其他總類的協(xié)議分析儀,包括嵌入式設(shè)備用的SDIO協(xié)議分析儀,QSPI協(xié)議分析儀及訓(xùn)練器,I3C協(xié)議分析儀及訓(xùn)練器,RFFE協(xié)議分析儀及訓(xùn)練器等等。我司還有代理SPMI協(xié)議分析儀及訓(xùn)練器,車載以太網(wǎng)分析儀,以及各種相關(guān)的基于示波器的解碼軟件和SI測(cè)試軟件。同時(shí),歐奧電子也有提供高難度焊接,以及高速信號(hào),如UFS,DDR3/DDR4,USBtypeC等高速協(xié)議抓取和分析的服務(wù)。邏輯分析儀基礎(chǔ)邏輯分析儀是一種類似于示波器的波形測(cè)試設(shè)備,它可以監(jiān)測(cè)硬件電路工作時(shí)的邏輯電平(高或低),并加以存儲(chǔ),用圖形的方式直觀地表達(dá)出來,便于用戶檢測(cè)和分析電路設(shè)計(jì)(硬件設(shè)計(jì)和軟件設(shè)計(jì))中的錯(cuò)誤。邏輯分析儀是設(shè)計(jì)中不可缺少的電子測(cè)試設(shè)備,通過它可以迅速地定位錯(cuò)誤、解決問題、達(dá)到事半功倍的效果。一、邏輯分析儀的產(chǎn)生和發(fā)展20世紀(jì)70年代初研制出微處理器,出現(xiàn)4位和8位總線,傳統(tǒng)示波器的雙通道輸入無(wú)法滿足8bit的觀察。微處理器和存儲(chǔ)器的測(cè)試需要不同于時(shí)域和頻域儀器,所以數(shù)域測(cè)試儀器應(yīng)運(yùn)而生。邏輯訓(xùn)練器廠家哪家好?歐奧電子!

序列步驟存儲(chǔ)總會(huì)覆蓋默認(rèn)存儲(chǔ),但只針對(duì)序列步驟存儲(chǔ)中特別指定的條件。處理默認(rèn)存儲(chǔ)和序列步驟存儲(chǔ)之間的時(shí)一定要謹(jǐn)慎。雖然設(shè)置邏輯分析儀很困難,但觸發(fā)函數(shù)可以降低此過程的難度。觸發(fā)函數(shù)是可以組合起來設(shè)置觸發(fā)的常用構(gòu)建塊。由于這些函數(shù)涵蓋了多數(shù)普通觸發(fā),因此通過選擇適當(dāng)?shù)暮瘮?shù)并將其填充到數(shù)據(jù)中即可設(shè)置觸發(fā)。下圖顯示了邏輯分析儀觸發(fā)用戶界面。請(qǐng)注意,觸發(fā)函數(shù)位于屏幕左側(cè)的一個(gè)醒目位置。圖21使用觸發(fā)函數(shù)通常,設(shè)置復(fù)雜觸發(fā)的難題是對(duì)問題進(jìn)行分解。換句話說,就是如何將復(fù)雜觸發(fā)映射到序列步驟、分支和布爾邏輯表達(dá)式。將問題分解為不同時(shí)發(fā)生的事件。這些事件對(duì)應(yīng)于序列步驟。掃描觸發(fā)函數(shù)列表,嘗試找出一些與步驟1中確定的事件相匹配的函數(shù)。將所有剩余事件分解為布爾邏輯表達(dá)式及其相應(yīng)操作。各個(gè)布爾邏輯表達(dá)式/操作對(duì)分別對(duì)應(yīng)于序列步驟中的一個(gè)單獨(dú)分支。請(qǐng)記住,可能存在只用于為序列步驟處理存儲(chǔ)限定的“存儲(chǔ)”分支。設(shè)置邏輯分析儀觸發(fā)與編寫軟件相徑庭。如果使用預(yù)定義的觸發(fā)函數(shù)和較早編寫的文檔完善的觸發(fā)來完成其他工作,就可降低設(shè)置邏輯分析儀觸發(fā)的難度。在沒有其他可用的資源時(shí),才需要編寫自己的觸發(fā)設(shè)置。后。SD協(xié)議分析儀/訓(xùn)練器找歐奧!福州EMMC協(xié)議分析儀品牌

UART邏輯分析儀/訓(xùn)練器找歐奧!SD協(xié)議分析儀費(fèi)用

整體功能雖然不能和專業(yè)儀器相比,但是用較低的成本來實(shí)現(xiàn)特定的功能,也是非常成功的設(shè)計(jì)。本文以下討論的邏輯分析儀,主要是指這類入門級(jí)設(shè)計(jì)。基于電腦并口的邏輯分析儀曾是主流,但是近年來電腦系統(tǒng)逐步不再配置并口,這類設(shè)計(jì)已經(jīng)成為明日黃花,還具有原理學(xué)習(xí)的價(jià)值。另一類的邏輯分析儀,是以低速單片機(jī)為基礎(chǔ)的。很多愛好者用PIC、AVR等常見單片機(jī)設(shè)計(jì)了自己的作品。但這類單片機(jī)邏輯分析儀的共同弱點(diǎn)就是采樣速度太慢,通常不超過1MHz。以USBIO芯片為基礎(chǔ)的入門級(jí)邏輯分析儀現(xiàn)在為流行。比如Saleaelogic,還有類似的USBee等。這類產(chǎn)品主要采用一個(gè)USBIO芯片,例如CYPRESS公司的CY7C68013A-56PVXC,所有的信號(hào)觸發(fā)和處理工作都是電腦上的軟件完成的,硬件部分就只是一個(gè)數(shù)據(jù)記錄儀。高采樣速度為24MHz。它們可以“無(wú)限數(shù)量”地采樣,因?yàn)樗械臄?shù)據(jù)都是存儲(chǔ)在電腦里的。目前一般多是8個(gè)通道,更多的通道數(shù)量會(huì)成比例地降低高采樣速度。這類產(chǎn)品構(gòu)造簡(jiǎn)單,方便易用,價(jià)格便宜,是調(diào)試單片機(jī)開發(fā)工作的好工具。它的缺點(diǎn)主要是采樣速度只有24MHz、8個(gè)通道,對(duì)于分析高速并行總線就不能勝任了。更進(jìn)一步的設(shè)計(jì),需要增加FPGA、SRAM等器件。SD協(xié)議分析儀費(fèi)用

- 潮州協(xié)議分析儀那家好 2025-06-24

- 珠海邏輯分析儀費(fèi)用 2025-06-24

- 溫州I2C/SPI分析儀費(fèi)用 2025-06-23

- 蘇州邏輯分析儀售價(jià) 2025-06-23

- 常州UFS分析儀報(bào)價(jià) 2025-06-23

- SD協(xié)議分析儀費(fèi)用 2025-06-23

- 廣州RFFE分析儀收費(fèi) 2025-06-23

- 中山EMMC分析儀廠家 2025-06-23

- 潮州邏輯分析儀 2025-06-23

- 揭陽(yáng)UART分析儀找哪家 2025-06-23

- 江蘇帶你了解遠(yuǎn)傳水表有什么類型 2025-06-24

- 單模BOTDR設(shè)備售價(jià) 2025-06-24

- 重慶智能防爆冰箱設(shè)計(jì) 2025-06-24

- 鹽城放心選鹽霧腐蝕試驗(yàn)箱加裝 2025-06-24

- 懸浮風(fēng)機(jī)激光對(duì)中價(jià)格 2025-06-24

- 湖南罐體稱重模塊定制 2025-06-24

- 震蕩波局部放電波形圖分析 2025-06-24

- 天津鉭膜片隔膜壓力表廠家 2025-06-24

- 廣州多工位多模金相鑲嵌機(jī)選型 2025-06-24

- 一體化超聲波液位計(jì)廠家直供 2025-06-24